SiFive 博客

来自 RISC-V 专家的最新洞察与深度技术解析

Introducing SiFive Insight

Access, Observe, Control

The term ‘debug’ has a storied history. It’s widely reported as being coined by computing pioneer, US Navy Rear Admiral Grace Hopper, when she removed a moth from Harvard’s Mark II computer in 1945. Use of the word bug can also be traced to the great inventor, Thomas Edison, from a letter he wrote in 1878. Whatever the origin, we all agree that we don’t want bugs in our systems, our hardware, our code.

With computer systems long past the size where physical inspection is feasible, and programming using wires or punch cards long gone, we need new methods. We need insight into the machine, the code, the operations happening millions of times per second right in front of us to create high-quality products, accurately and quickly.

An Industry Leading RISC-V Trace & Debug Portfolio

Today, SiFive are pleased to announce SiFive Insight, a portfolio of trace and debug IP, software, and tools, to make the development of new SiFive RISC-V products efficient and simple. Observing product operation is critical for developing secure, efficient systems. These trace and debug features allow access to system state information, and even modification, to better understand the system’s operational flow.

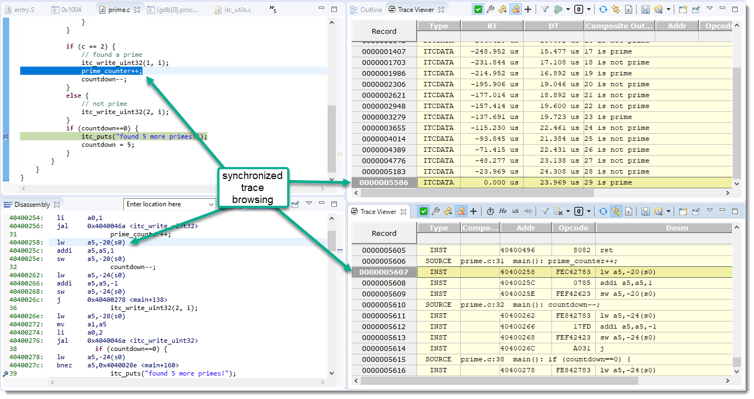

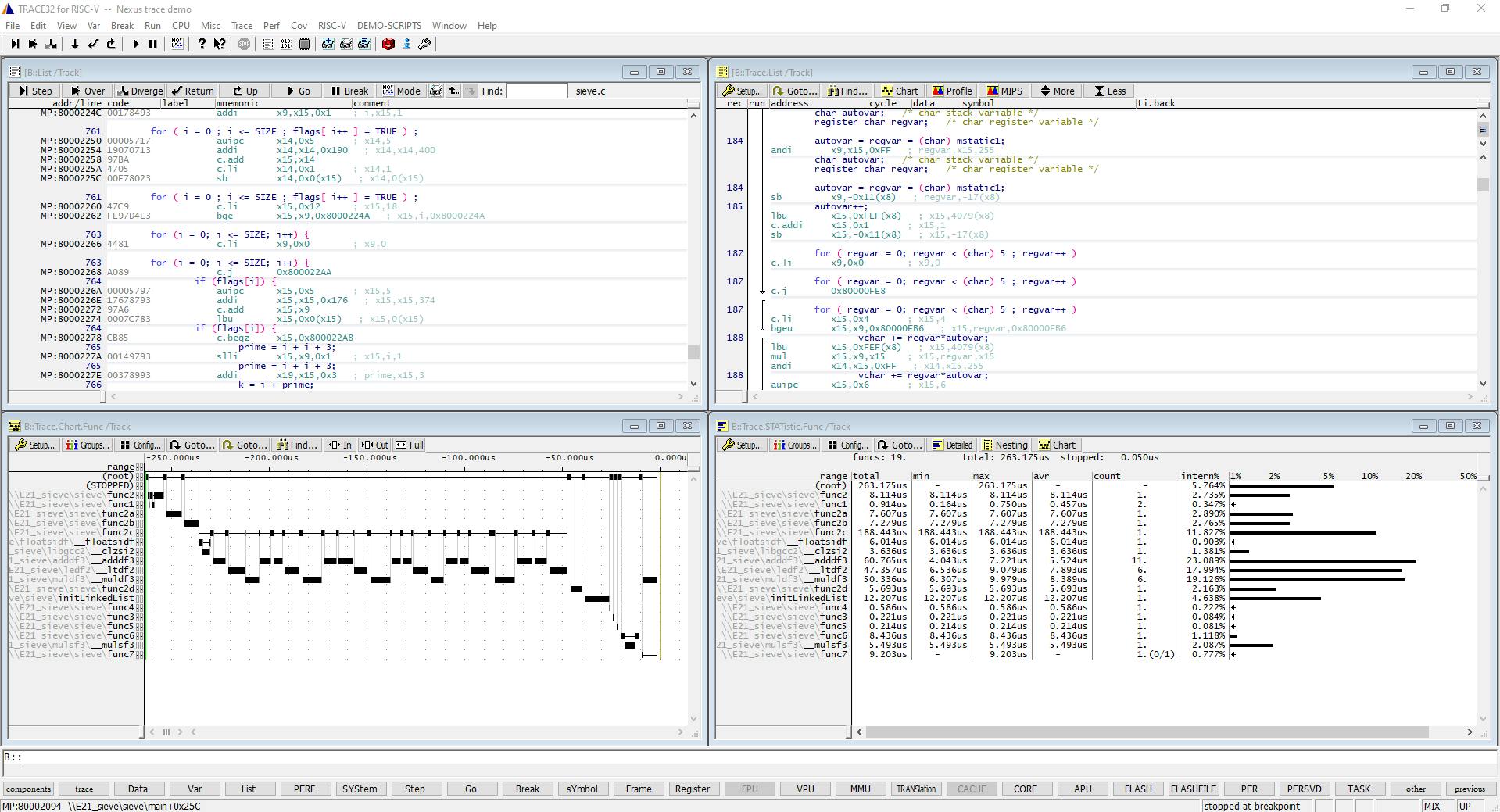

The capability to trace processor instruction execution step-by-step, and examine the contents of debug logs gives us the abilities we need to observe, access, and control system operation during development.

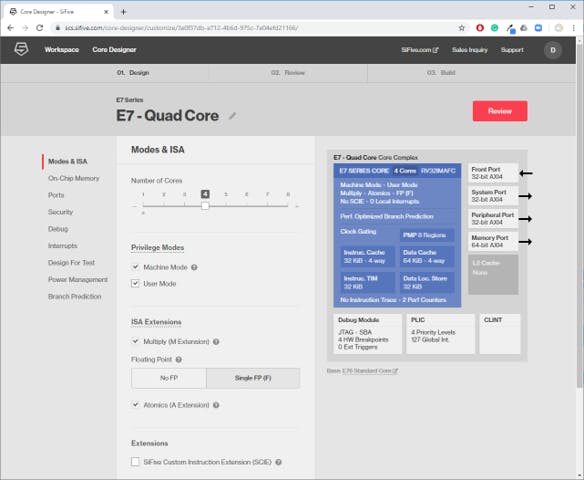

SiFive Insight is the first RISC-V core with pre-integrated debug and trace offering. SiFive Insight reduces complexity by offering a single-vendor solution that is lightweight and simple to integrate into SoC designs based on SiFive RISC-V processor Core IP. Uniquely, SiFive Insight supports Arm® Coresight™ to enable simple adoption and ease of use in a heterogenous SoC development environment.

SiFive Insight is pre-integrated and verified in a single deliverable, to offer a range of debug and trace functions as standard. From run-control to advanced multi-core trace in a heterogeneous core complex, SiFive Insight can be easily configured using the award-winning SiFive Core Designer to suit your needs.

All SiFive cores include the ability to be configured with up to 16 hardware triggers. Hardware triggers can stop the processor on the execution of an instruction or the read or write of a memory location. Furthermore, hardware triggers can be used to control trace collection. These triggers can be combined to support arbitrary ranges. In addition to core triggers, SiFive Insight supports a configurable number of external triggers allowing for external events to trigger a debug halt.

SiFive Insight is compatible with Nexus 5001™ trace specification standards, and is fully supported by the SiFive Freedom Studio integrated developer environment (IDE). Compatibility with Nexus 5001™ trace also ensures compatibility with leading developer tools. SiFive cores support the recently ratified RISC-V Processor Trace standard. The RISC-V Foundation trace and debug working group is evaluating Nexus 5001™ trace as an additional standard to be ratified. SiFive works closely with our ecosystem partners to enable them with the latest SiFive Insight technology, ensuring that they are well-positioned to support application developers and chip designers.

IAR Systems

Lauterbach

Lauterbach

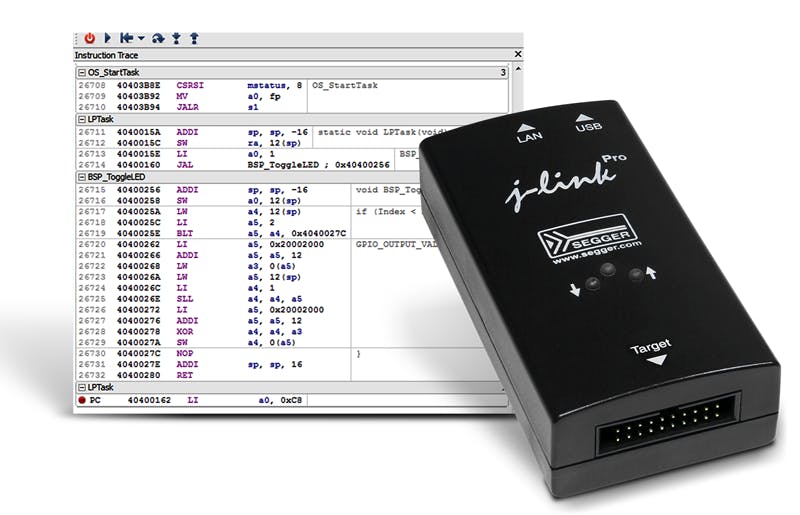

SEGGER

SEGGER

"SEGGER J-Link offers full support for the new SiFive Insight debug and trace IP, including the Nexus based trace implementation. With SEGGER J-Link the trace data can be read from on-chip memory, yielding back trace, execution counts, code profiling and code coverage information" - SEGGER Microcontroller GmbH

Market Momentum

Industry analysts forecast 62.4 billion RISC-V cores will be deployed in the next 5 years. SiFive’s portfolio of products, tools, and expertise will ensure the development of your new market-focused product is secure, efficient, and free of bugs.