SiFive 博客

来自 RISC-V 专家的最新洞察与深度技术解析

Three New Core Series Now Available in SiFive Core Designer

SiFive Core Designer (SCD) unlocks new possibilities by enabling engineers to explore the architectural design space of a CPU. With our Software-as-a Service (SaaS) application, customers can create and customize RISC-V core IP -- from their laptops.

Working within a Core Series (a “class” of Core paired with a specific microarchitecture) customers can rapidly create a range of cores at different design points, run software applications on FPGA bitstreams, simulate with RTL, and ultimately determine the best custom silicon for their product. Explore SiFive Core Designer.

INTRODUCING QUARTERLY UPDATES

Today we are announcing the SiFive Quarterly Update Program, which is designed to “stream” SiFive’s latest innovations and features to customers. With today’s Q2 2019 engineering update, we’re expanding the available Core Series in SiFive Core Designer and adding a number of compelling new core IP features.

ADDING THREE NEW CORE SERIES TO SCD

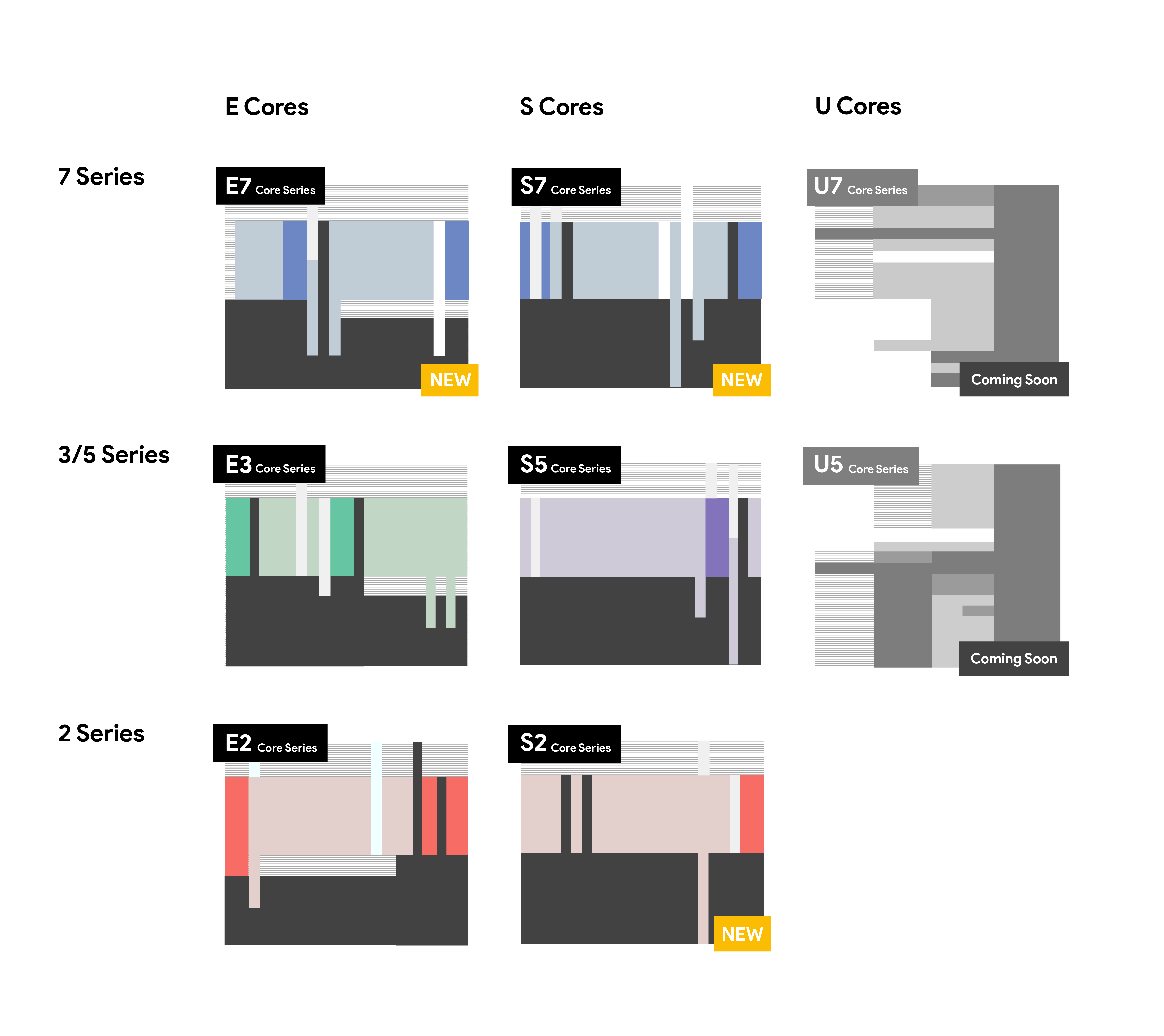

With the addition of the E7, S7, and S2 Core Series to SiFive Core Designer, E and S cores (32-bit and 64-bit embedded cores, respectively) can be customized across all SiFive microarchitectures. U cores (64-bit application cores) will be added to SCD in a subsequent quarterly update.

7 Series: E7, S7

With an 8-stage, dual-issue superscalar pipeline and a scalable throughput provided by 8 cores per cluster, the 7 Series is SiFive’s highest-performance microarchitecture. Read more about the 7 Series.

The E7 and S7 Core Series offer 32-bit and 64-bit embedded processors targeting applications that require high performance while maintaining energy efficiency.

2 Series: S2

Edge SoCs (System on Chip) face the diverse requirements of real-time latency, deterministic capability, and stringent power constraints. The 2 Series enables SoCs to have an always-on, low power CPU that can be combined with high-performance CPUs that switch on only when applications demand performance, such as in voice-activated smart devices. The 2 Series can be configured to be as small as just 13,500 gates (in RV32E form).

The S2 Core Series brings a 64-bit architecture to SiFive’s smallest microcontrollers. An S2 core is just half the size of a similarly configured S5 core. Read more about the S2 Core Series.

NEW CORE IP FEATURES

This quarter, we’ve rolled in a new set of core IP features, which are available and configurable from SiFive Core Designer.

New to all Core Series:

- SCIE (SiFive Custom Instruction Extension): Add RISC-V-compatible custom instructions

New to 2 Series:

- RV32E (RISC-V ISA Extension): Create a minimal E2 core (as small as 13.5k gates)

- μInstruction Cache: More efficient performance in memory-constrained designs

New to 3, 5 Series:

- Multicore: Choose up to 8 cores

- Floating Point: Single-precision and double-precision FP

- L2 Cache: optional second-level cache

New to 7 Series:

- Multicore: Choose up to 8 cores

- Fast IO: Maximizes IO throughput

- DLS (Data Local Store): Quick memory access for the Data Bus

- ITIM (Instruction Tightly-Integrated Memory): Quick memory access for the Instruction Bus

Read more about core IP features included in the Q2 engineering update.

ENHANCED CORE DESIGNER DEVELOPMENT KIT

We’ve included the Freedom E SDK (and Freedom Metal software examples) in every custom core Development Kit built by the Core Designer. As part of the Q2 engineering update, we’ve added the following examples:

- Benchmarks: Dhrystone and Coremark examples permit replication of SiFive benchmark scores

- Multicore Hello: Demonstrates booting a multicore target

- User Mode: Demonstrates entering user-mode via Freedom Metal API calls

Now, along with Freedom Studio, our Eclipse-based IDE, it’s never been easier to develop software for cores built by SiFive Core Designer. Read more about our software toolchain in the Q2 engineering update software blog.

SIFIVE SHIPS -- EVERY QUARTER

Rolling up SiFive’s products into a single update each quarter ensures that customers receive a complete end-to-end hardware/software development experience that regularly delivers innovation. We’re looking forward to shipping powerful new features in SiFive Core Designer as part of the Q3 2019 engineering update.