SiFive 博客

来自 RISC-V 专家的最新洞察与深度技术解析

Making It Easy To Get It Right

Today, SiFive is excited to announce the general availability of the Q3 2019 Engineering Update, packed with new features, tools, and improvements. In the first SiFive quarterly update, we discussed the transition from the “Information Age” to the “Experience Age.” In the Q3 Engineering Update, SiFive is delivering on our customer experience mantra: “Make It Easy” and “Get It Right.” - two principles at the heart of our Sales, FAE, and Engineering mindset for supporting and enabling our customers.

As the complexity of software continues to grow, the ability to quickly and efficiently write and debug software is critical to realize the fast time to markets necessary for IoT, Storage, Industrial, and Mission Critical markets as well as early silicon bring-up.

The focus of the Q3 2019 engineering update is adding Nexus 5001™ Instruction Trace capabilities across the SiFive Core IP portfolio. Nexus 5001™ is a mature and open industry standard supporting trace of embedded processors.

Making It Easy

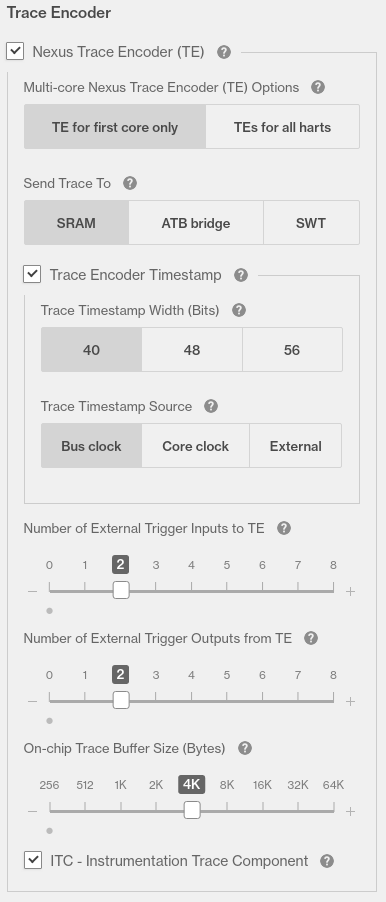

Configuring a SiFive Core IP project with advanced trace capabilities can now be performed in SiFive Core Designer. The core complex design is configured completely in SiFive’s cloud environment and delivered pre-integrated and verified in a single package saving you time, money, and engineering resources.

SiFive is also open-sourcing a cross-platform, C++ based, Nexus 5001™ Trace decoder software for RISC-V in order to ease integration into existing debug and trace environments. The latest release of Freedom Studio uses this software to display Instruction Trace streams intermixed with source code directly in the eclipse environment.

Getting It Right

By using Nexus 5001™ trace, SiFive processors are supported by a number of industry supported tools, including those provided by IAR, Lutenbach, and SEGGER.

Trace can be sent to a dedicated trace SRAM buffer which can be read anytime by a debugger. Nexus 5001™ trace packets may be bridged to an AMBA® ATB interface to ease integration into existing designs, as well as off chip using the Serial Wire Trace protocol.

The Nexus 5001™ trace encoders also support a configurable timestamp interface as well as the ability to both send and receive external triggers. In addition to the trace encoders, we are also adding an Instrumentation Trace Component (ITC). The ITC is a memory mapped peripheral which allows software to inject messages directly into the trace stream; printf for trace. This is especially useful for debugging large and complex software.

SiFive Core Designer

In the Q3 release we are introducing 64-bit Linux capable U5 and U7 Core Series to SiFive Core Designer allowing for customization of all SiFive Core IP to be done from your browser.

SiFive E7-Series Core IP included in SiFive Core Designer now offers optional double-precision floating point (RV32D) capabilities. The following advanced debug features have been integrated into SiFive Core Designer for all SiFive Core IP:

- Instruction Trace Encoder with Crash Detection

- Trace funnel for combining traces from multiple sources

- Debug Halt-On-Reset feature

- Instrumentation Trace with serial-wire output

Additionally, SRAM extraction options are available in SiFive Core Designer to help configure tailored cores to exacting specifications.

These small but mighty improvements in SiFive Core Designer show SiFive’s commitment to continuous improvement to the development of modern SoC designs for all applications.

Summary

The SiFive Q3 2019 engineering update incorporates a broad and welcome set of new features and improvements. We know our Customers will appreciate the new capabilities and can’t wait to hear about the new designs and solutions our robust, scalable approach to modern SoC design enables. Best of all, the new improvements can be tested on your Arty A7-100T FPGA test platform after configuring a core complex in SiFive Core Designer and using the latest version of Freedom Studio.