SiFive 博客

来自 RISC-V 专家的最新洞察与深度技术解析

Supporting A World Leading RISC-V IP Portfolio

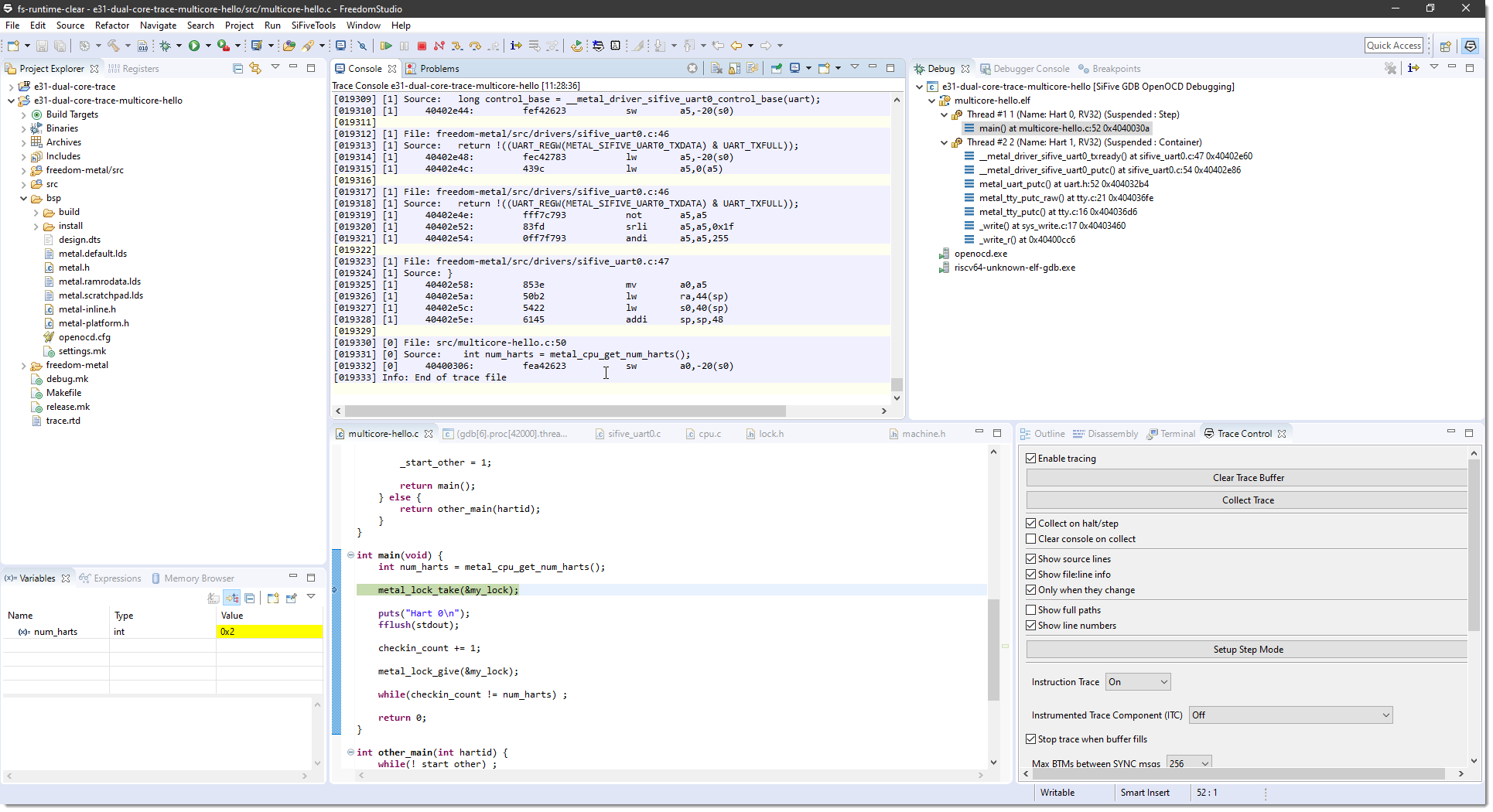

The second SiFive quarterly engineering release has arrived, and includes some great new Trace & Debug features. Static source code analysis may not offer a complete view of real world operation. Real time analysis enabled via tracing permits a deeper insight into the interactions of software and hardware to accelerate development, debug, validation of modern, configurable SoC designs.

A major focus of the Q3 Engineer Update was adding support for Nexus 5001™ compliant instruction trace. SiFive is pleased to contribute an open-sourced cross-platform, C++ based, Nexus 5001™ Trace decoder software for RISC-V. The latest release of Freedom Studio makes use of this software to display Instruction Trace streams intermixed with source code directly in the eclipse environment.

Freedom Everywhere SDK

To enhance Freedom Studio further, the ability to more easily switch between Freedom E SDK environments has been updated. SiFive Core IP assets can be imported directly to generate Freedom E SDK projects, also greatly enhancing workflow.

The Freedom E SDK bare-metal example program library has been expanded, including demonstrations of how to perform Cache Maintenance Operations as well as expanded CLIC and PLIC interrupt examples; and the SiFive HiFive Rev 1 B now includes a new simulate makefile target to automatically start up a QEMU simulation and QEMU BSP for the SiFive U54. To speed up test and integration processes, SiFive conveniently provides QEMU binaries to avoid the need to build from source. In keeping with our open-source values, the SiFive Freedom Tools repository contains the toolchains and utilities source for this release.

Freedom Unleashed SDK

Open-source contributions are a core value for SiFive, driving the contribution of an updated Freedom U SDK to an Open Embedded workflow, to enable community adoption of the SiFive HiFive Unleashed platform with an industry standard embedded linux workflow.

The initial release includes a meta-sifive layer with support for the HiFive Unleashed and QEMU. The meta-sifive layer supports creating a demo image for the HiFive Unleashed board with the expansion board from Microsemi, a Microchip company, which supports a desktop environment and a few demonstration game titles. SD Card images can be easily created following standard Open Embedded workflows with complete instructions directly in the Freedom U SDK repository. We have also made HiFive Unleashed SD Card images available for download directly on our HiFive Boards page for those who just want to flash and go.

SiFive will continue to improve Open Embedded support through future quarterly updates, while access to the previous buildroot based environment will continue to be available in Freedom U SDK under the archive/buildroot tag.

Summary

With these open-source contributions and key new feature support including in the SiFive Core IP portfolio, the time has never been better to engage for your next project. Reach out today and turn your next dream SoC into a reality with the world leader in RISC-V, SiFive.